در سال ۲۰۲۶، صنعت نیمههادی جهان شاهد یک تحول ساختاری بیسابقه است: معماری متنباز RISC-V موفق شده ۲۵ درصد از بازار جهانی تراشهها را فتح کند و برای اولین بار در چهار دهه اخیر، انحصار دوگانه ARM و x86 را به چالش جدی بکشد. این مقاله تحلیلی جامع و فوقتخصصی از این انقلاب محاسباتی ارائه میدهد و نشان میدهد چگونه آزادی طراحی، هزینه صفر لایسنس، و مقاومت ذاتی در برابر تحریمهای تکنولوژیکی، RISC-V را به مهمترین تحول ساختاری صنعت نیمههادی در دهه ۲۰۲۰ تبدیل کرده است. در قلب هر پردازندهای — از تراشه کوچک داخل ساعت هوشمند تا ابرپردازندههای چند میلیون دلاری دیتاسنترهای انویدیا — یک "زبان مادری" وجود دارد که معماری مجموعه دستورالعمل (ISA) نام دارد. برای بیش از چهار دهه، دنیای پردازندهها تحت سلطنت مطلق دو ISA انحصاری بود: x86 (متعلق به اینتل و AMD) و ARM (متعلق به ARM Holdings). هر دوی این معماریها "مالکیتی" هستند و شرکتها مجبورند هزینههای لایسنس هنگفتی بپردازند. اما مهمتر از هزینه مالی، "محدودیت طراحی" است — شما نمیتوانید به دلخواه دستورات سفارشی برای شتاب عملیات خاص به پردازنده خود اضافه کنید. RISC-V (تلفظ: ریسک-فایو) یک معماری ISA کاملاً متنباز و آزاد است که در سال ۲۰۱۰ توسط محققان دانشگاه کالیفرنیا-برکلی ابداع شد. برخلاف ARM و x86، هیچ شرکتی مالک RISC-V نیست و استفاده از آن کاملاً رایگان است. مزیت کلیدی RISC-V، "ماژولاریتی" آن است: معماری پایه فوقالعاده ساده است (تنها ۴۷ دستورالعمل پایه)، اما مهندسان میتوانند هر تعداد "اکستنشن سفارشی" که بخواهند به آن اضافه کنند — اکستنشنهای بُرداری برای شتاب AI، اکستنشنهای رمزنگاری، اکستنشنهای امنیتی و غیره. در سال ۲۰۲۶، RISC-V دیگر یک پروژه آکادمیک نیست بلکه یک جنگ صنعتی تمامعیار است. کوالکام اعلام کرد بخش قابلتوجهی از هستههای پردازشی نسل بعدی خود را بر پایه RISC-V طراحی خواهد کرد. گوگل نیز از هستههای RISC-V در تراشههای Tensor استفاده میکند. اما بزرگترین بازیگر، چین است — تحریمهای آمریکا باعث شده چین تمام قوای صنعتی خود را روی RISC-V متمرکز کند. برآورد Counterpoint Research نشان میدهد RISC-V در سال ۲۰۲۶ حدود ۲۵ درصد از بازار جهانی تراشههای IoT و Edge را فتح کرده است. یکی از مهیجترین جنبههای RISC-V، پذیرش رسمی اکستنشن V (Vector Extension) است که به پردازندهها اجازه میدهد عملیات بُرداری و ماتریسی — ستون فقرات الگوریتمهای AI — را با سرعت بسیار بالا اجرا کنند. برخلاف ARM که SVE2 را به صورت ثابت ارائه میدهد، اکستنشن V در RISC-V کاملاً پارامتریک و قابل تنظیم است. یعنی شرکتها میتوانند شتابدهندههای AI فوقتخصصی بسازند که دقیقاً برای بارکاری خاص آنها بهینهسازی شده باشد. شاید ژئوپلیتیکیترین جنبه RISC-V، نقش آن در دور زدن تحریمهای تکنولوژیکی باشد. از آنجا که RISC-V یک استاندارد باز است، هیچ دولت یا شرکتی نمیتواند دسترسی به آن را محدود کند. RISC-V توسط بنیاد بینالمللی RISC-V اداره میشود که مقر آن به سوئیس منتقل شده تا از فشارهای ژئوپلیتیکی مصون بماند. شرکتهای ایرانی و روسی که از دسترسی به تراشههای ARM و x86 محروم شدهاند، با استفاده از طرحهای RISC-V و کارخانههای Foundry چینی، قادر به طراحی و تولید پردازندههای بومی خود هستند. برای ایران، RISC-V یک فرصت استراتژیک بینظیر است. دانشگاهها و شرکتهای دانشبنیان ایرانی میتوانند بدون نیاز به هیچ لایسنس خارجی، هستههای پردازشی RISC-V را طراحی کنند. این مسیر برای کاربردهایی مانند کنترلرهای صنعتی، سامانههای نظامی، تجهیزات مخابراتی و تراشههای امنیتی بانکی بسیار واقعبینانه است. شروع از RISC-V و ساخت اکوسیستم نیمههادی بومی، تنها مسیر واقعگرایانه برای استقلال تکنولوژیک ایران در حوزه تراشهسازی محسوب میشود. حکم نهایی: RISC-V در سال ۲۰۲۶ نه یک تهدید فوری بلکه یک زلزله تکتونیکی آهسته است که پایههای انحصار ARM/x86 را تخریب میکند. در بازار IoT و Edge AI، RISC-V برنده قطعی است. در بازار موبایل و لپتاپ، هنوز ۳ تا ۵ سال فاصله دارد. در بازار سرور و AI، رقابت در حال شروع است. آزادی طراحی، هزینه صفر لایسنس، و مقاومت ذاتی در برابر تحریمها آن را به مهمترین تحول ساختاری صنعت نیمههادی در دهه ۲۰۲۰ تبدیل کرده است.

Breaking the ARM/x86 Duopoly: How the Open-Source RISC-V Architecture Captured 25% of the Global Chip Market in 2026, Revolutionizing AI Accelerators, Hardware Security, and Geopolitical Silicon Independence Forever.

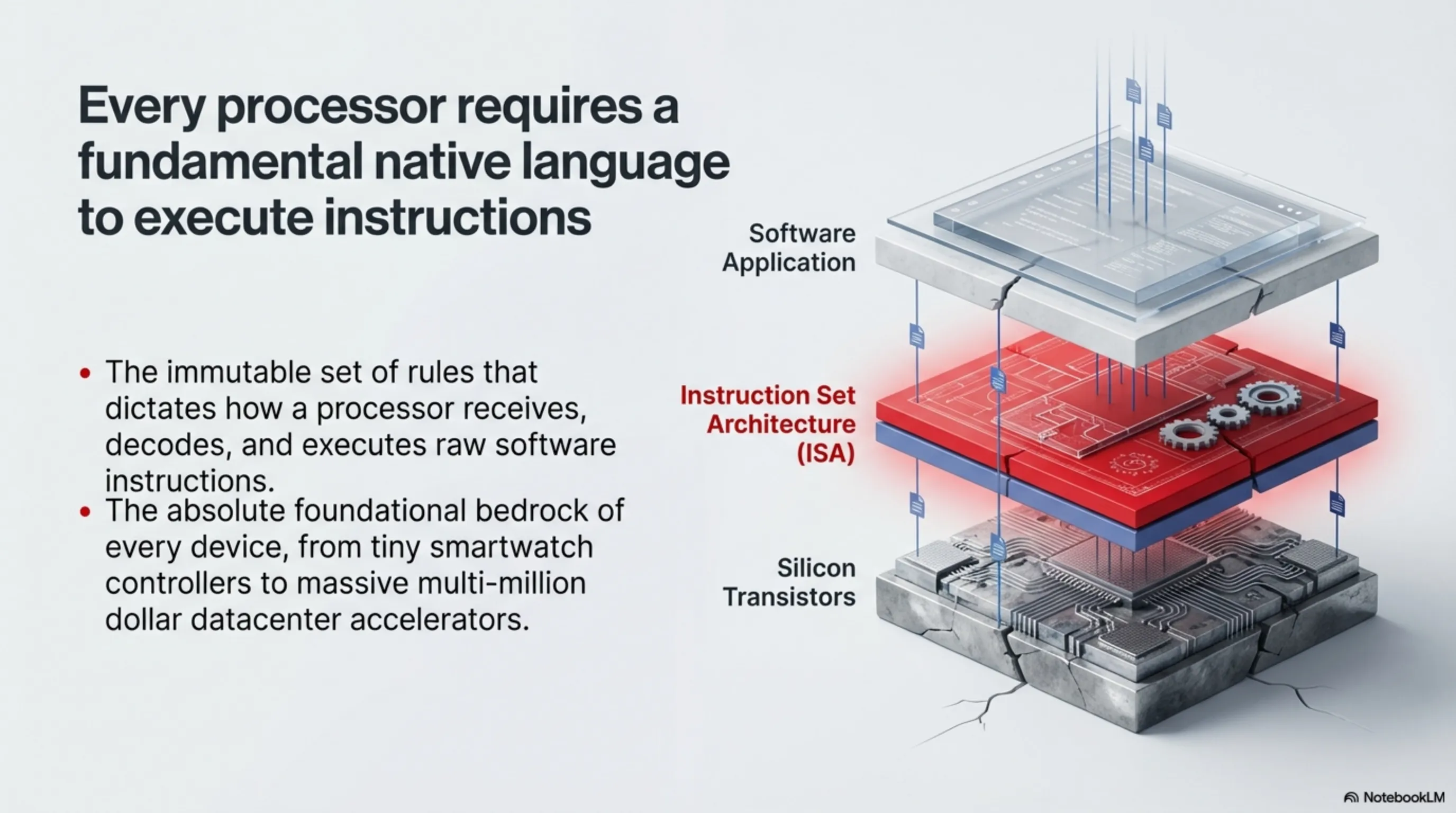

Part 1: Introduction — What Is an Instruction Set Architecture (ISA) and Why It Matters

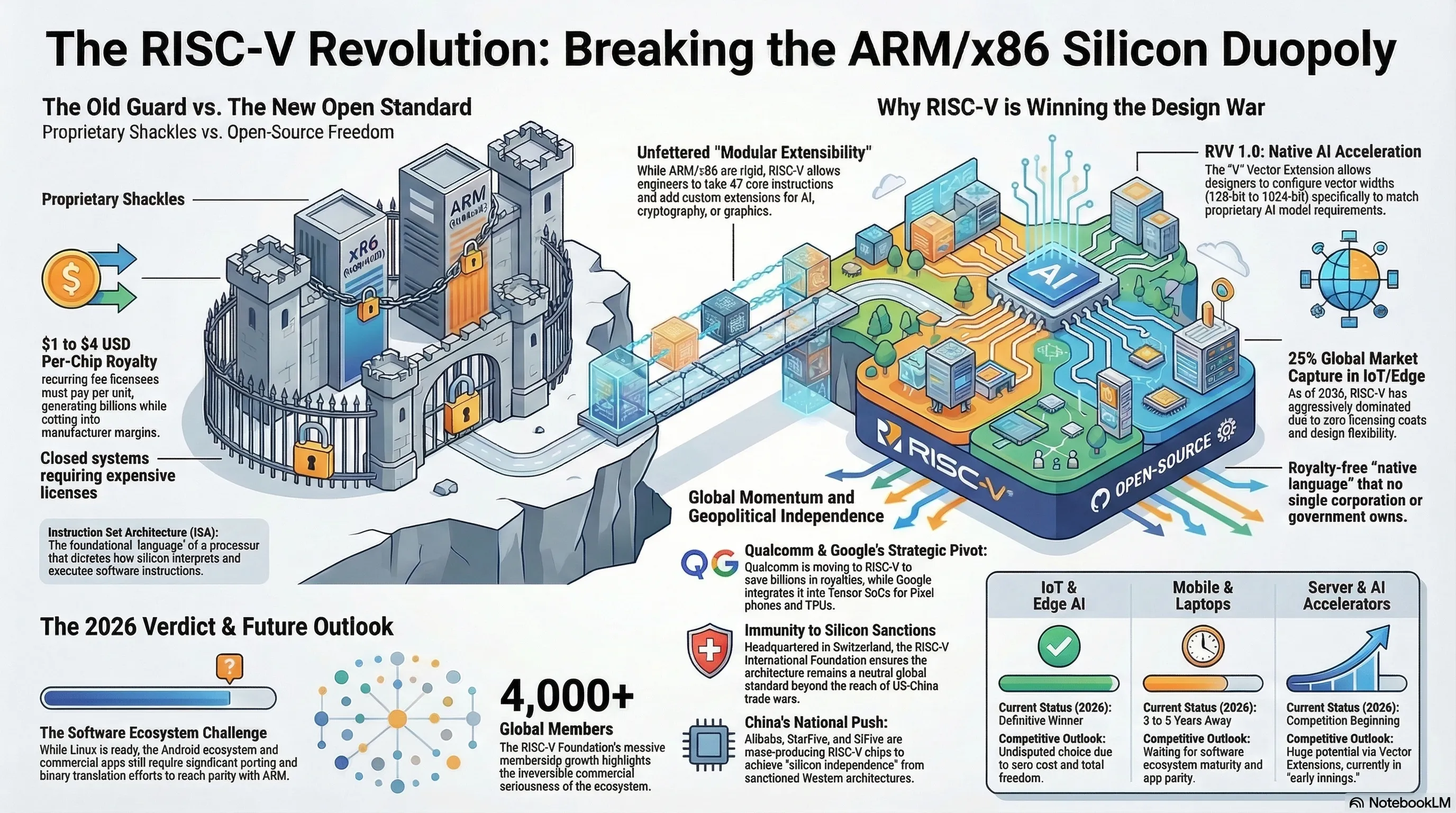

At the absolute foundational bedrock of every single processor ever manufactured—from the microscopically tiny controller embedded deep within your consumer smartwatch to the multi-million dollar supercomputing accelerators physically housed within Nvidia's colossal datacenter complexes—there exists a fundamental, immutable "native language" that the specific processor exclusively comprehends and obeys. This foundational language is formally designated the "Instruction Set Architecture" (ISA). The ISA precisely, rigidly dictates exactly how a processor physically receives, decodes, interprets, and subsequently executes raw software instructions fed into its silicon transistors. For over four brutally contested decades, the entire global semiconductor universe existed under the absolute, unchallenged monarchical reign of precisely two deeply proprietary ISAs: x86 (exclusively owned and jealously guarded by the unyielding duopoly of Intel and AMD), which maintained an iron fist over the desktop, laptop, and server markets; and ARM (exclusively owned by ARM Holdings, currently a subsidiary of Japan's SoftBank Group), which aggressively monopolized the mobile smartphone, tablet, and low-power embedded processor markets.

Both of these architectures are fundamentally, legally "Proprietary." This implies that if a corporation—whether a massive conglomerate like Samsung or a fiercely ambitious Chinese tech giant like Huawei—desires to design its own custom processor, it is legally compelled to pay staggeringly expensive licensing royalties to ARM Holdings. The situation surrounding x86 is arguably far more restrictive: fundamentally, only Intel and AMD possess the legal right to design and manufacture x86 processors, and no other company on the planet is permitted to construct one. This rigid, deeply entrenched duopoly is being questioned with profound, existential seriousness for the first time in 2026, and the entirely disruptive agent driving this fundamental challenge is the explosive, revolutionary emergence of the fully open-source RISC-V architecture.

Part 2: The ARM/x86 Duopoly — Licensing Costs and Design Shackles

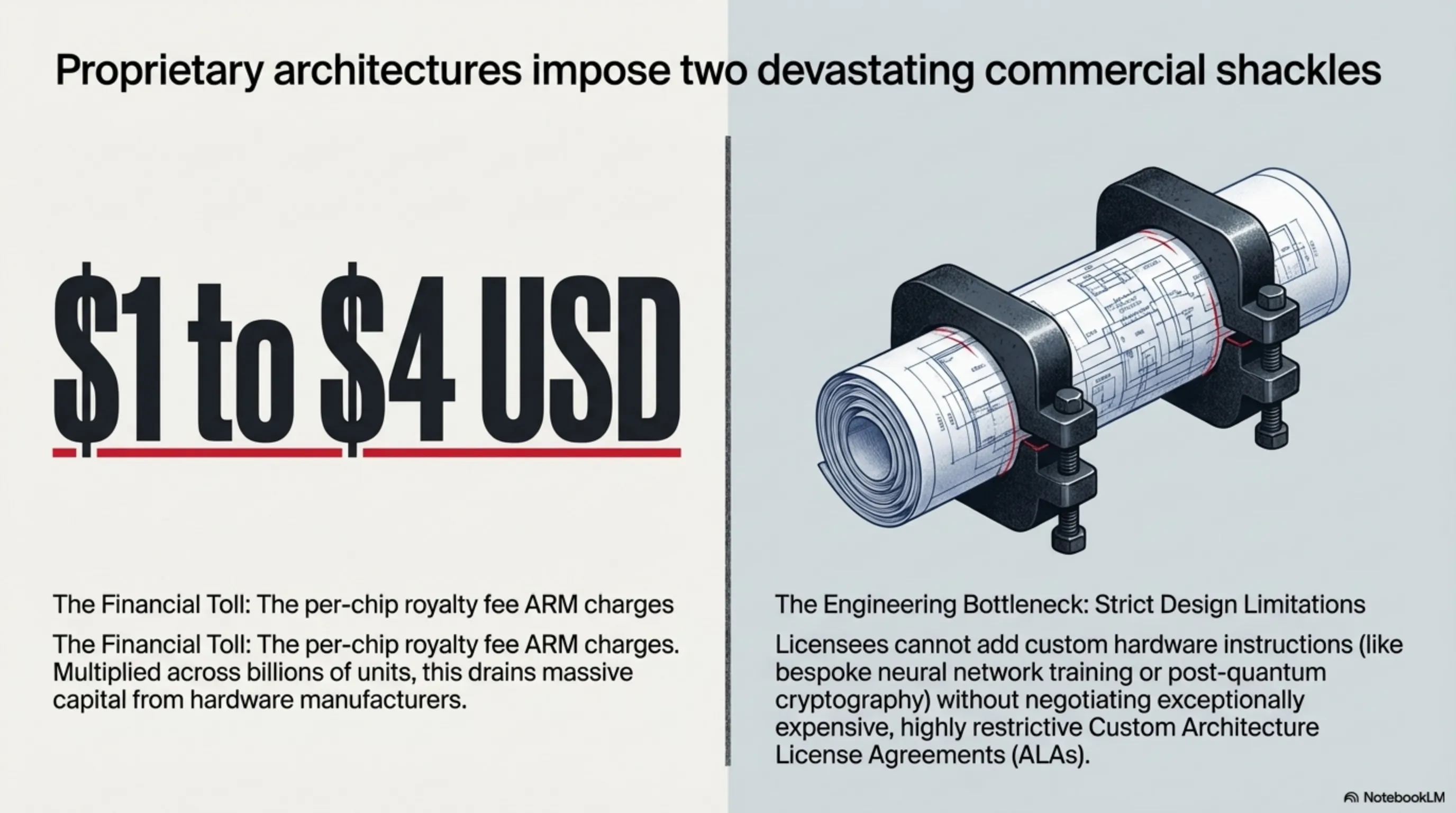

ARM Holdings operates a unique, extraordinarily profitable commercial model: the company itself does not manufacture any physical chips whatsoever. Instead, it meticulously designs core processor architectures (commonly known as CPU "IP blocks") and then aggressively sells expensive commercial licenses for these pre-designed blueprints to other hardware manufacturers. Apple, for its M-series and A-series silicon; Qualcomm, for its ubiquitous Snapdragon SoCs; Samsung, for its Exynos processors; and MediaTek, for its Dimensity chips—all must legally pay significant, recurring per-unit licensing royalties to ARM. According to publicly audited financial reports from 2025, the per-chip royalty fee charged by ARM ranges between approximately $1 and $4 USD, which, when multiplied across the billions of units shipped annually by ARM's licensees, generates multi-billion dollar recurring revenue streams.

However, the financial cost alone does not capture the full magnitude of the restriction. Far more damaging than the monetary expense is the severe "Design Limitation" imposed by the license. When a corporation purchases an ARM architecture license, it is contractually bound to rigorously comply with ARM's rigid architectural rules and specifications. The licensee fundamentally cannot, at its own discretion, freely add entirely new, custom hardware instructions specifically designed to accelerate proprietary computational tasks—such as custom neural network training acceleration or advanced post-quantum cryptographic operations—to their processor unless they negotiate exceptionally expensive, highly restrictive Custom Architecture License Agreements (ALAs). This structural limitation, in an era where practically every serious technology corporation urgently requires hyper-specialized, bespoke AI hardware accelerators, has mutated into a deeply paralyzing, commercially devastating engineering bottleneck.

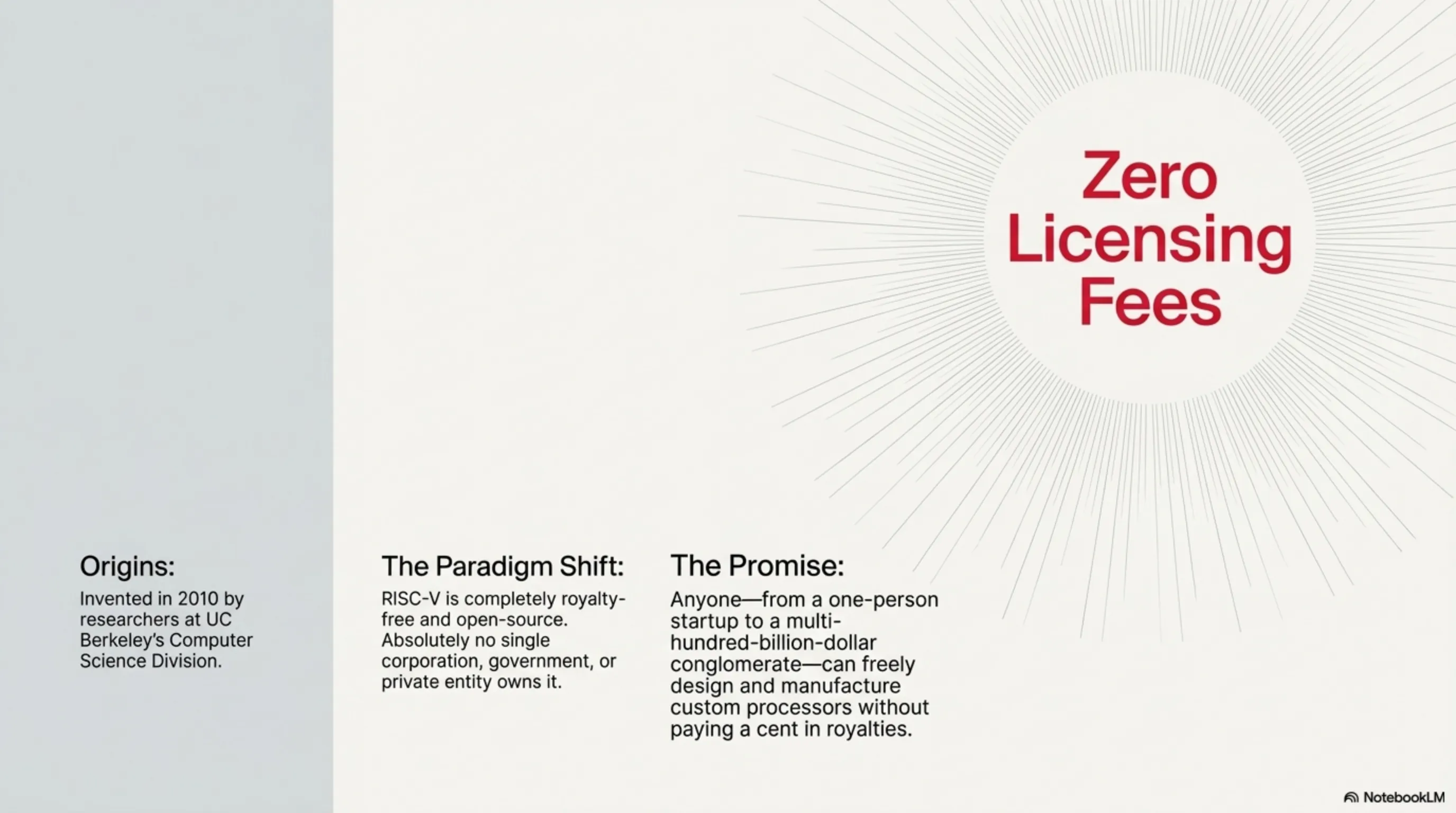

Part 3: RISC-V — The Royalty-Free, Open-Source ISA

RISC-V (pronounced "Risk-Five") is an entirely open-source, completely royalty-free Instruction Set Architecture (ISA) originally invented in 2010 by a team of brilliant researchers operating within the Computer Science Division at the University of California, Berkeley. In stark, radical contrast to both ARM and x86, absolutely no single corporation, government, or private entity on the planet legally "owns" RISC-V. Its utilization is entirely, unconditionally free, and any entity—from a solitary one-person hardware startup operating out of a cramped garage to a multi-hundred-billion-dollar Silicon Valley conglomerate—can legally, freely design and commercially manufacture a completely custom RISC-V processor without paying even a solitary cent in licensing royalties to any organization.

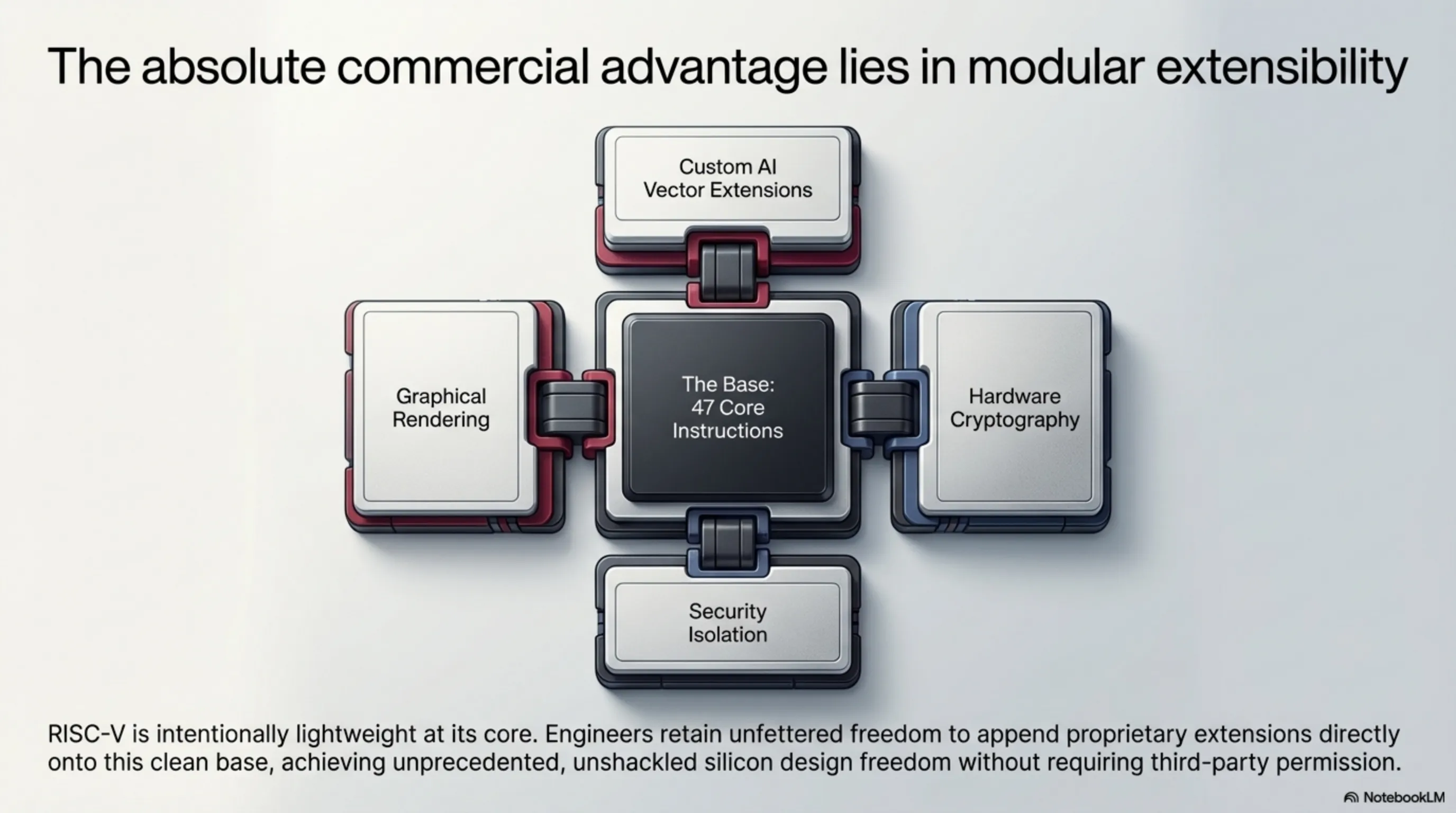

The absolutely critical, commercially devastating competitive advantage of RISC-V resides in its extraordinary "Modular Extensibility." The foundational base RISC-V ISA is intentionally, aggressively minimalist and lightweight, comprising a mere 47 core instructions. However, engineers retain the absolute, unfettered freedom to append any number of custom, proprietary "Extensions" directly onto this clean base: custom Vector Extensions specifically designed for massively accelerating AI matrix operations, custom hardware cryptographic extensions, custom security isolation extensions, custom graphical rendering extensions, and practically any other specialized computational pipeline the designer can conceive of. This unprecedented, unshackled level of silicon design freedom is historically unmatched and represents the singular, dominant reason behind the explosive, almost viral popularity of RISC-V throughout 2026.

Part 4: Corporate Titans Go RISC-V — Qualcomm, Google, and China's Massive Investments

In 2026, RISC-V has definitively, violently graduated from its origins as a modest academic research project and has aggressively transformed into a full-scale, multi-front industrial war. Qualcomm—a corporation that for years remained deeply, profitably dependent on ARM licensing for its enormously successful Snapdragon SoC family—publicly announced its strategic decision to aggressively redesign a substantial, commercially significant portion of its next-generation processing cores entirely upon a custom RISC-V foundation. The primary commercial justification: permanently liberating itself from the billions of dollars in cumulative annual ARM licensing payments and simultaneously gaining complete, absolute, unfettered design freedom to deeply integrate custom AI acceleration instructions directly at the silicon level.

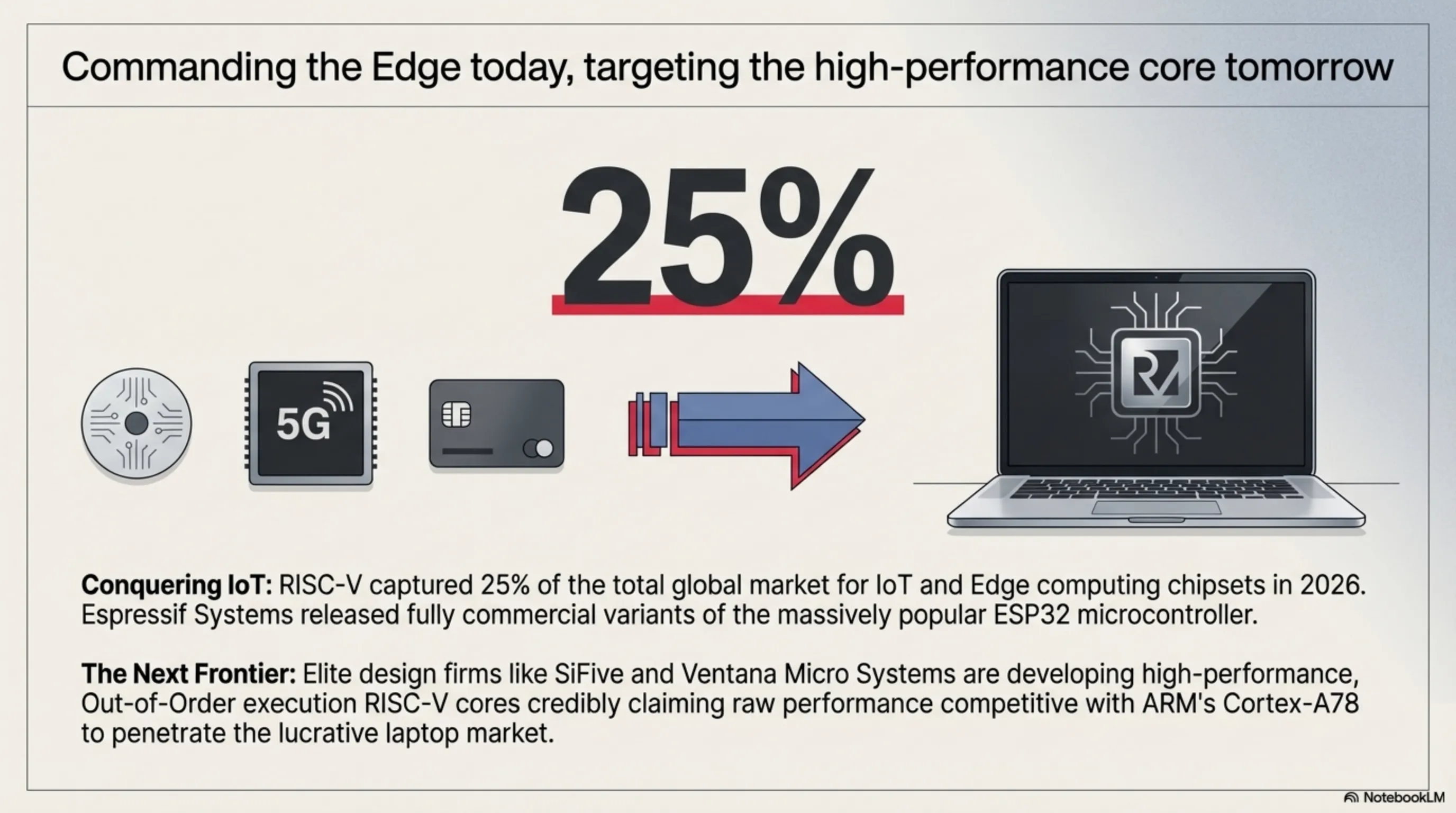

Google has similarly integrated RISC-V cores into the control subsystems of its internally developed Tensor Processing Units (TPUs) and Tensor mobile SoCs powering its Pixel smartphone family. However, the single most massively consequential player driving the RISC-V explosion is China. The sweeping, intensifying cascade of American technology sanctions that have severely restricted Chinese corporations' access to advanced ARM blueprints and cutting-edge x86 processors has functionally forced the entirety of China's massive domestic semiconductor apparatus to concentrate its formidable national industrial resources almost exclusively onto RISC-V. Companies such as Alibaba's T-Head division (manufacturer of the Xuantie RISC-V cores), StarFive, and the American-headquartered but Asian-fabricated SiFive are aggressively executing mass production of commercially viable RISC-V processors. Exhaustive market analysis from Counterpoint Research definitively estimates that RISC-V has brutally captured approximately 25 percent of the total global market for IoT and Edge computing chipsets in 2026.

Part 5: Custom Vector Extensions for AI Acceleration

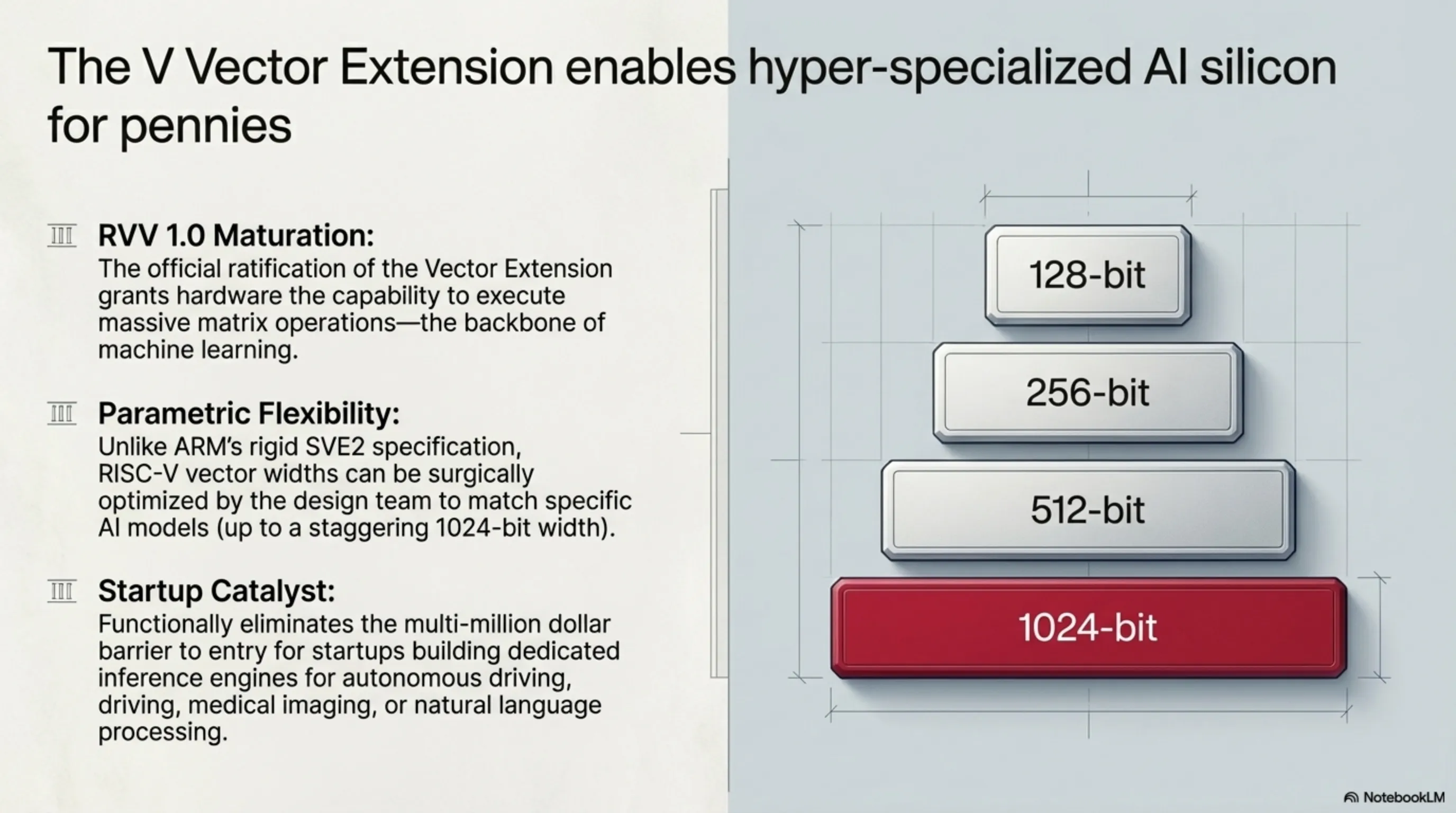

One of the most technically electrifying aspects of RISC-V in 2026 is the official ratification and industrial maturation of the "V" Vector Extension (RVV 1.0). This critical extension grants RISC-V processors the native hardware capability to execute massive vectorized and matrix operations—the absolute computational backbone of all modern machine learning and deep learning algorithms—at brutally high throughput rates. Unlike ARM, which delivers its SVE2 (Scalable Vector Extension 2) as a fixed, rigid, non-modifiable hardware specification, the RISC-V V Extension is inherently fully parametric and deeply configurable.

This means a silicon design team can architect their RISC-V core so that the physical vector width precisely matches the exact computational requirements of their specific target AI model: 128-bit, 256-bit, 512-bit, or even a staggering 1024-bit vector width. This degree of silicon design flexibility is absolutely, historically unprecedented in the commercial semiconductor domain. It empowers corporations to construct hyper-specialized AI accelerator chips precisely, surgically optimized for their exact proprietary workloads, without paying any licensing fee whatsoever to any third-party entity. For startups building dedicated inference engines for autonomous driving, medical imaging, or natural language processing, this RISC-V flexibility functionally eliminates the multi-million dollar barrier to entry that ARM's restrictive licensing model traditionally imposed.

Part 6: Geopolitical Silicon — Breaking Hardware Sanctions via Open Architecture

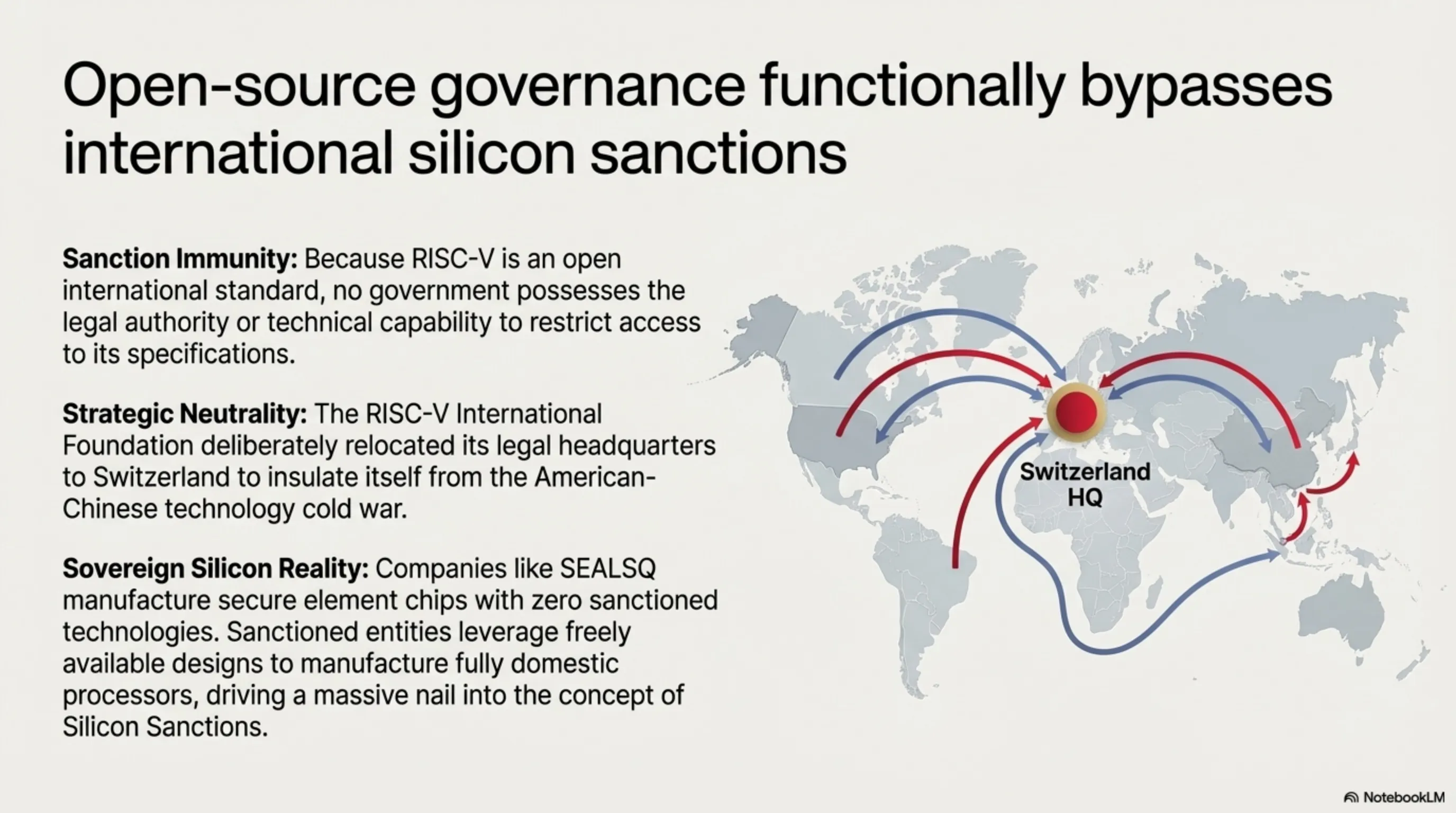

Perhaps the single most geopolitically explosive aspect of RISC-V in 2026 is its structural role in fundamentally undermining and circumventing technology export sanctions. Because the RISC-V ISA is legally, structurally an open international standard, no government and no corporation possesses the legal authority or technical capability to restrict access to its foundational specifications. Unlike ARM, which is centrally controlled and commercially gatekept by a single specific corporation (ARM Holdings, ultimately subject to UK and American regulatory jurisdiction), RISC-V is governed by the independent RISC-V International Foundation, which deliberately relocated its legal headquarters to Switzerland specifically to insulate itself from the intense geopolitical pressures emanating from the American-Chinese technology cold war.

Companies such as SEALSQ (specializing exclusively in hardware-based IoT security) are actively manufacturing RISC-V-based secure element chips whose entire supply chain is meticulously, legally constructed to contain zero sanctioned technologies. Furthermore, corporations operating within sanctioned nations—including Iran, Russia, and specific Chinese entities blacklisted from accessing advanced ARM and x86 architectures—can legally utilize freely available RISC-V designs combined with Chinese-operated fabrication foundries such as SMIC to independently design and manufacture fully domestic, sovereign processors. RISC-V has essentially, functionally hammered a massive nail into the coffin of the entire concept of "Silicon Sanctions," powerfully demonstrating that in the emerging era of open-source silicon, restricting any nation's access to advanced processor technology is becoming exponentially more difficult and arguably futile.

Part 7: RISC-V in IoT and Edge Computing — Conquering Billions of Connected Devices

The most commercially successful deployment vector for RISC-V as of 2026 resides firmly within the Internet of Things (IoT) and Edge Computing domains. Small, ultra-low-power, aggressively inexpensive RISC-V chipsets are now actively deployed within billions of connected physical devices globally: ranging from industrial smart sensors and intelligent home automation controllers to advanced 5G communication modules and hardware Secure Elements embedded within financial banking cards. Companies such as Espressif Systems—the massively popular manufacturer of the globally adopted ESP32 microcontroller family—have released fully commercial RISC-V based variants of their product lines.

Looking forward through 2026, the aggressive next frontier for RISC-V expansion targets penetration into the far more lucrative, intensely competitive laptop and server processor markets. While no fully commercial, mainstream RISC-V laptop exists as of the current date, elite semiconductor design firms such as SiFive and Ventana Micro Systems are actively developing high-performance, Out-of-Order execution RISC-V cores that credibly claim raw execution performance competitive with ARM's Cortex-A78 and potentially beyond. The true inflection point will dramatically arrive when the first commercially viable RISC-V-based laptop—fully capable of running mainstream Linux distributions and potentially Android—ships to paying consumers.

Part 8: The Software Ecosystem Challenge — Linux, Android, and Developer Toolchains

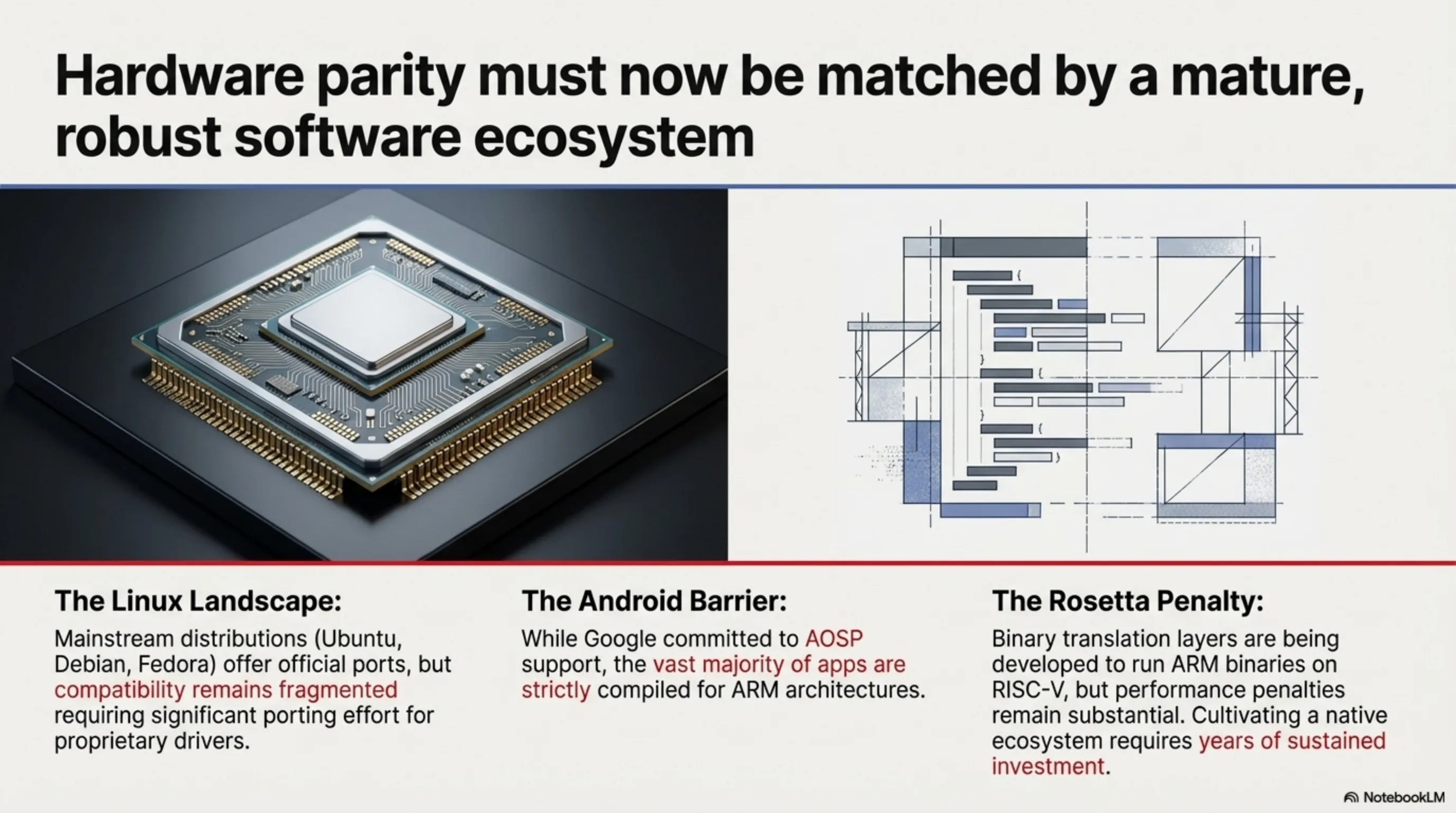

While RISC-V's hardware advantages are undeniable, the architecture faces a critical challenge that ARM spent decades solving: building a mature, comprehensive software ecosystem. As of 2026, mainstream Linux distributions including Ubuntu, Debian, and Fedora offer official RISC-V ports, but software compatibility remains fragmented. Many commercial applications, proprietary drivers, and specialized development tools that "just work" on ARM and x86 require significant porting effort for RISC-V.

The Android ecosystem presents an even steeper climb. While Google has committed to RISC-V support in AOSP (Android Open Source Project), the vast majority of Android apps are compiled for ARM architectures. Binary translation layers—similar to Apple's Rosetta 2—are being developed to run ARM binaries on RISC-V processors, but performance penalties remain substantial. For RISC-V to truly challenge ARM in the mobile and laptop markets, it needs not just hardware parity but a thriving app ecosystem where developers actively target RISC-V as a first-class platform. This transformation will require years of sustained investment from major players like Google, Qualcomm, and the RISC-V Foundation itself.

Part 9: Wall Street and Venture Capital — The RISC-V Investment Frenzy

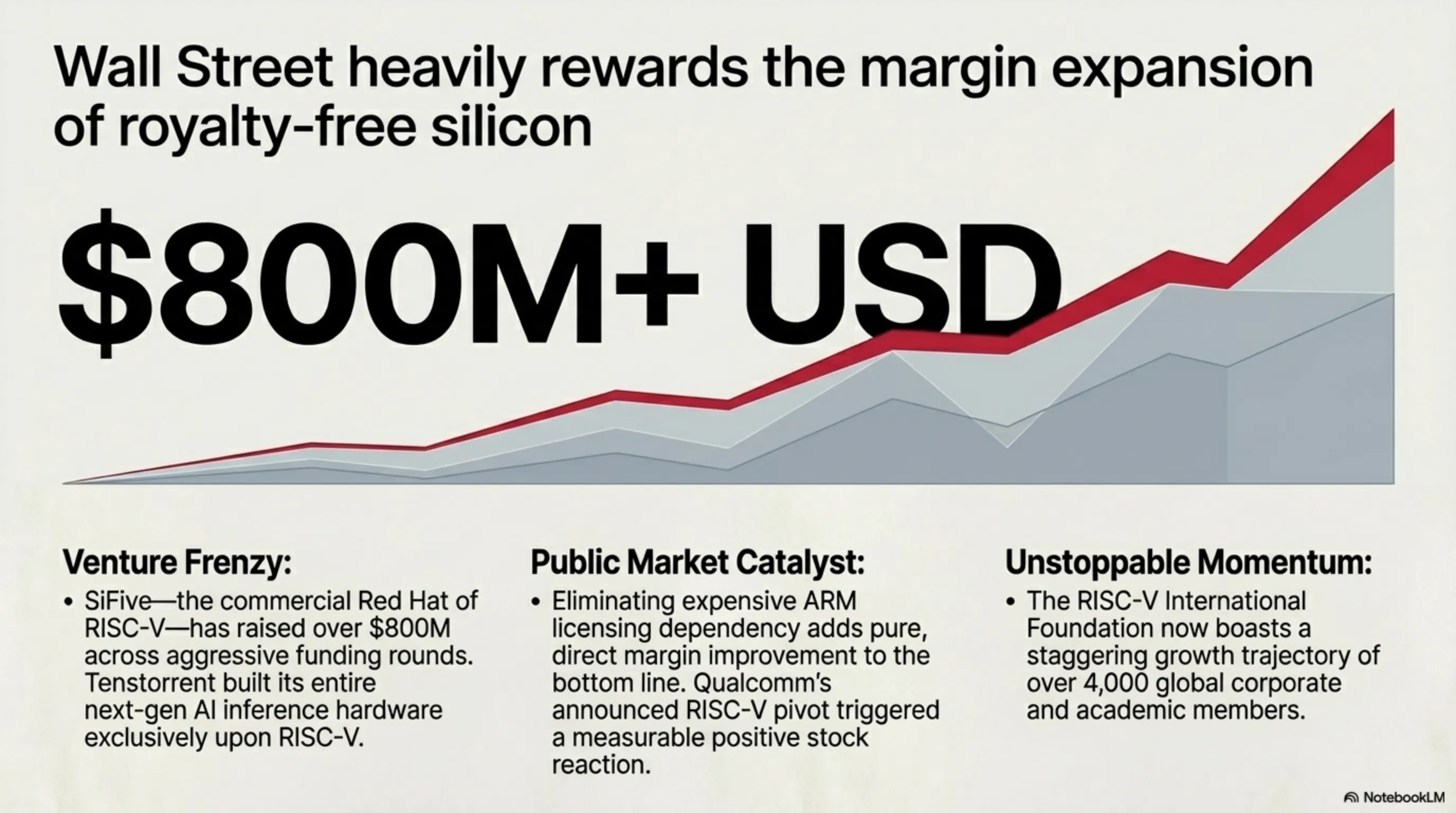

From a pure financial perspective, RISC-V has transformed into one of the absolute hottest, most aggressively contested investment themes across Wall Street and the global venture capital ecosystem throughout 2026. SiFive—widely considered the commercial "Red Hat of RISC-V"—has raised cumulative funding exceeding $800 million USD across multiple aggressive funding rounds. Tenstorrent, the AI-focused chip design company founded by legendary processor architect Jim Keller, has built its entire next-generation AI inference hardware architecture exclusively upon RISC-V foundations. The RISC-V International Foundation itself now boasts over 4,000 corporate and academic members globally—a staggering growth trajectory demonstrating the absolute, irreversible commercial seriousness of this ecosystem.

For public market investors monitoring semiconductor equities, the RISC-V value proposition is uniquely compelling. Any company successfully displacing its expensive ARM licensing dependency with royalty-free RISC-V cores immediately adds pure, direct margin improvement directly onto its bottom line. This is precisely why Qualcomm's publicly announced RISC-V pivot triggered a measurable, sustained positive stock reaction—Wall Street mathematically calculated the billions in cumulative licensing savings and rewarded the strategic decision aggressively.

Final Editorial Verdict: Does RISC-V Actually Kill ARM?

IoT and Edge AI Market: RISC-V is the Definitive Winner (Zero licensing costs + total design freedom = the undisputed ideal choice for billions of connected devices.)

Mobile and Laptop Market: 3 to 5 Years Away (The software ecosystem and core performance have not yet reached the commercial maturity levels established by ARM's decade-long head start.)

Server and AI Accelerator Market: Competition Just Beginning (The RISC-V Vector Extensions possess enormous untapped potential but remain in the early innings.)

Final Tekin Analysis: RISC-V in 2026 is not an immediate, acute threat to ARM's established dominance—it is a slow, inexorable tectonic earthquake steadily demolishing the foundations. Design freedom, zero licensing costs, and inherent structural immunity to export sanctions have collectively transformed RISC-V into the single most significant structural transformation in the semiconductor industry of the 2020s.

RISC-V Revolution Image Gallery